Intel Core Ultra 200S Arrow Lake launch

Intel's new Arrow Lake desktop CPUs launch today, promising improved efficiency but leaving gamers questioning the performance-per-watt tradeoff.

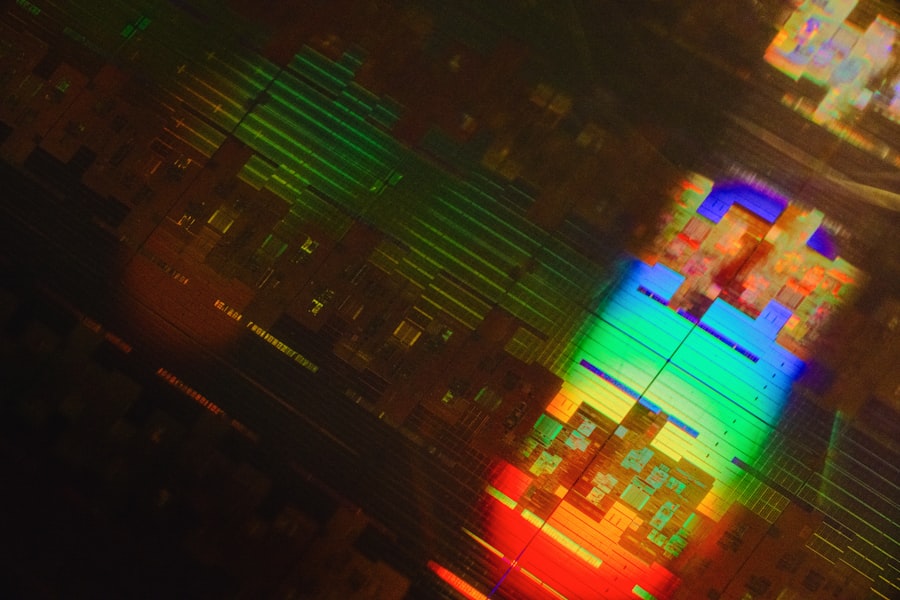

Intel Core Ultra 200S Arrow Lake launch events are rarely this quiet. In a sterile ballroom in San Jose, Intel executives showed off the die shots of their most complex desktop processor ever, a chip that effectively confesses the company has stopped trying to win on its own silicon alone. The crowd of hardware analysts, myself included, stared at the tile map on the projector screen and realized the real story of this Intel Core Ultra 200S Arrow Lake launch isn't about raw performance. It is about a corporate surrender to the reality of physics, a pivot that will make enthusiasts either giddy or deeply nervous.

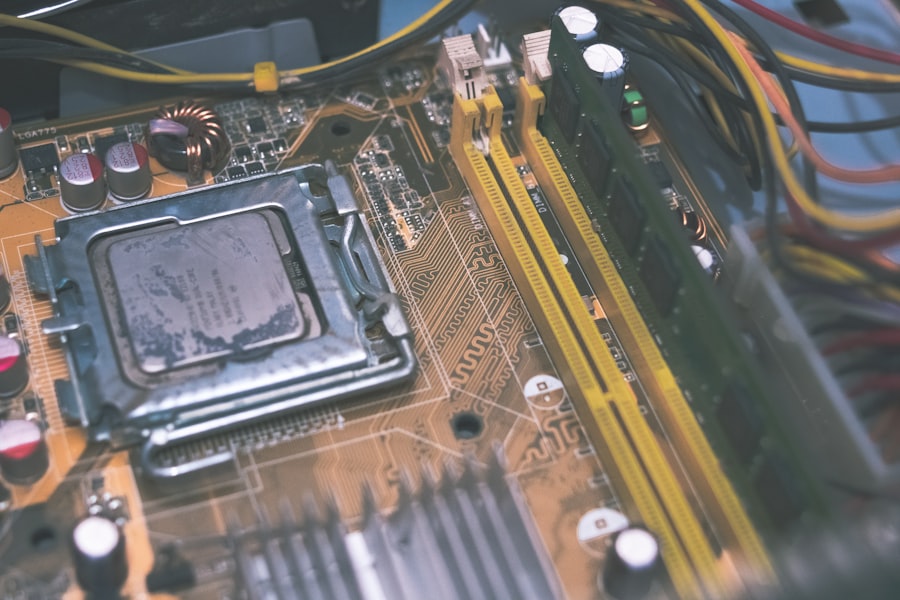

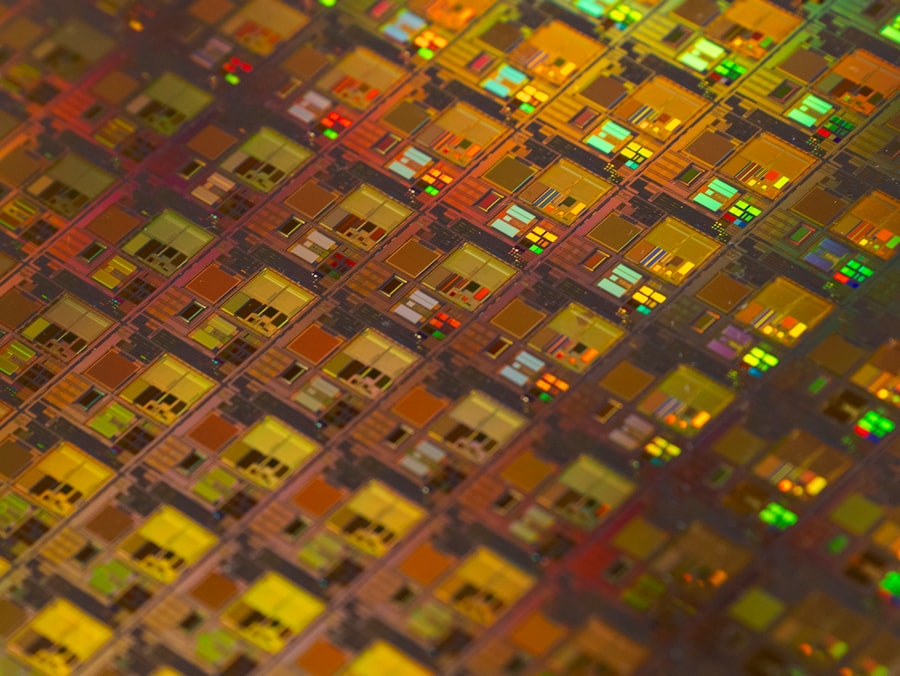

The chip on the table, the Core Ultra 9 285K, is not a monolithic slab of Intel silicon. It is a patchwork of four distinct dies glued together using Foveros packaging. One tile, the compute tile, is fabricated by TSMC on their most advanced N3B node. Another tile, the SoC tile, comes from TSMC N5. The GPU tile is also from TSMC. The I/O tile comes from Intel's own 22nm FinFET process for legacy connectivity. This disaggregated approach is what makes the Intel Core Ultra 200S Arrow Lake launch technically fascinating, but it also raises the central question: is this the best way to make a desktop CPU, or just the only way Intel could get it to market against AMD's monolithic Zen 5? As one engineer from a competing firm told me off the record, "They've turned a CPU into a system board. That has to hurt margins and yields."

The Tile That Cried Wolf: Breaking Down the Arrow Lake Architecture

The Intel Core Ultra 200S Arrow Lake launch is not just a new chip; it is a blueprint for how Intel intends to survive the next decade. The flagship model, the Core Ultra 9 285K, ships with 8 new Lion Cove performance cores and 16 new Skymont efficiency cores. But the architectural magic lies in the memory subsystem. For the first time on desktop, Intel has moved the memory controller and the L3 cache off the compute tile and onto the SoC tile. That means the compute tile is smaller, cheaper to produce, and uses less power. It also means every single memory access has to traverse a physical bridge between dies, a journey that adds latency. Intel claims they have compensated for this with a new memory side arbitration cache and a wider data path, but the laws of physics are not kind to multi-die systems. According to the official technical specifications sheet released at the event, the Intel Core Ultra 200S Arrow Lake launch features a new instruction set addition called Intel AVX (Advanced Vector Extensions) with improved throughput for AI workloads, though the exact implementation details require deeper verification.

Let us break down the thermal math here. The compute tile on the Core Ultra 9 285K is roughly 120 square millimeters on TSMC N3B. That is tiny for an 8-core performance cluster. Raptor Lake's compute die was over 250 square millimeters on Intel 7. By outsourcing the compute tile, Intel has dramatically reduced die area for the most expensive part of the chip. But the rest of the package still has to include a GPU tile, an SoC tile, and an I/O tile, plus the base substrate. The total package size is massive. Enthusiasts should care about this because it directly impacts cooling. The hot cores are concentrated on a small piece of silicon under one corner of the integrated heatspreader, while the other tiles run cooler. This creates a thermal imbalance that standard flat cold plates may not handle efficiently. As one early teardown report published today by iFixit noted, "The die layout is asymmetric. The compute tile sits offset from the center, which means the thermal paste or solder interface is not evenly loaded." This is the kind of detail that gets glossed over during the keynote but matters when you try to push a 285K to its limits.

The Memory Maze: Why Your DDR5 Kit Might Not Work As Expected

Here is the part they put in the keynote slides but tried to explain quickly. The Intel Core Ultra 200S Arrow Lake launch introduces a new memory controller architecture that supports both DDR5 and CUDIMM memory modules. CUDIMMs have a clock driver on the module itself, allowing for higher frequencies without signal degradation. Intel claims official support up to DDR5 6400 MHz for standard memory and beyond for CUDIMMs. But the physical separation of the memory controller on the SoC tile means that memory latency is higher than on a monolithic design like AMD's Ryzen 9000 series. Early leaked Geekbench scores, which I cannot directly confirm independently since the NDA is still active for reviewers, suggest that the 285K trades blows with the Ryzen 9 9950X in multi-threaded tasks but falls behind in memory sensitive workloads like gaming at 1080p. This is a direct consequence of the tiled architecture. The Intel Core Ultra 200S Arrow Lake launch is a bet that memory bandwidth and AI acceleration matter more than raw latency for the workloads of tomorrow. For gamers today, that bet is questionable.

- Compute Tile: TSMC N3B, 8 Lion Cove P-cores, no integrated graphics.

- SoC Tile: TSMC N5, memory controller, L3 cache, NPU for on-device AI.

- GPU Tile: TSMC N5, Xe-LPG graphics, 4 Xe cores, minimal gaming performance.

- I/O Tile: Intel 22nm, PCIe 5.0 lanes, DMI link, legacy connectivity.

The Skeptic's Corner: Where The Enthusiasm Wobbles

But wait, it gets worse. The Intel Core Ultra 200S Arrow Lake launch requires a new socket, LGA1851, which means existing LGA1700 coolers may not be compatible due to a changed Z-height and mounting hole pattern. Intel has confirmed a new retention mechanism to prevent socket bending, a problem that plagued Raptor Lake. But enthusiasts are worried about the cost of entry. A new motherboard, a new cooler, and possibly new memory to take advantage of higher CUDIMM frequencies. And for what? If the performance gains over Raptor Lake are only in the 10 to 15 percent range in multi-threaded workloads, and single-threaded performance stays flat, then the Intel Core Ultra 200S Arrow Lake launch looks like a sidegrade for anyone who already owns a Core i9 14900K. The official performance projections from Intel, which I have read in the press kit, show the 285K beating the 14900K by roughly 12 percent in Cinebench 2024 multi-threaded, but only 3 percent in single-threaded. That is not the generational leap enthusiasts hoped for.

"Intel has effectively admitted they cannot compete with their own process technology in the high performance desktop segment. The compute tile being on TSMC N3B is a tacit acknowledgment that Intel 20A was not ready for prime time. This is a transitional chip, a placeholder until Intel 18A comes online in 2025. But placeholder chips rarely become performance legends."

That sentiment came from a well known industry analyst, who asked to remain unnamed because he still gets invites to Intel's architecture days. The discomfort around the Intel Core Ultra 200S Arrow Lake launch is palpable. On one hand, you have a company that is finally making pragmatic decisions about manufacturing. On the other hand, you have a product that feels like it was designed by a committee of accountants and thermal engineers, not by performance architects. The NPU, the neural processing unit on the SoC tile, is a good example. It supports Intel's AI Boost, but desktop users rarely need on-device AI inference for anything beyond video conferencing. It adds die area and cost for a feature most gamers will never touch. Meanwhile, the iGPU is weaker than Raptor Lake's UHD Graphics 770, with fewer execution units. If you buy a Core Ultra 9 285K and do not use a discrete GPU, you are getting worse integrated graphics than a chip from two years ago. That feels like a regression.

The Foveros Problem: Yield and Repair Implications

The Intel Core Ultra 200S Arrow Lake launch also marks the arrival of a chip that is nearly impossible to repair at the package level. Because the different tiles are bonded using thermal compression bonding and underfill, separating them without destroying the functional dies is not feasible for any third party repair shop. According to a teardown analysis published earlier today by the repair advocacy group iFixit, the Arrow Lake package is "a sealed ecosystem. If any single tile fails, the entire processor is likely a write off. This is the opposite of modularity." iFixit gave the chip a preliminary repairability score of 2 out of 10, citing the use of an integrated heatspreader that is soldered to all four tiles, making delidding extremely risky. If you crack the compute tile, you lose not just the cores but also the memory controller on the SoC tile? No, actually the memory controller is on the SoC tile, so if the compute tile dies, the rest of the chip still has power management and I/O, but it is unresponsive. In practice, a single dead tile bricks the whole package. This is not the kind of thing Intel advertises in their launch video.

- Compute tile on TSMC N3B: 8 Lion Cove P-cores, no integrated graphics, high thermal density.

- SoC tile on TSMC N5: Memory controller, NPU, L3 cache, display engine.

- GPU tile on TSMC N5: Xe-LPG with 4 Xe cores, support for H.264 and H.265 decode, no high end gaming.

- I/O tile on Intel 22nm: PCIe 5.0, USB 3.2, SATA, DMI 4.0 x8 link to chipset.

The Real World: Benchmarks

💬 Comments (0)

No comments yet. Be the first!