Apple M5 chip production enters early stage

TSMC's N3P node yields for Apple's M5 chip are reportedly exceeding expectations, signaling a major performance jump.

Apple M5 chip production enters early stage, and the first engineering validation samples have already left TSMC’s Fab 18 in southern Taiwan. I have spent the past 36 hours on the phone with supply chain sources, former Apple silicon engineers, and semiconductor analysts who describe a chip that is both a staggering technical leap and a potential repair nightmare. This is not a preview. This is a live update from the bleeding edge of silicon fabrication, and the story is already getting complicated.

The Cold Open: What Actually Happened in the Last 48 Hours

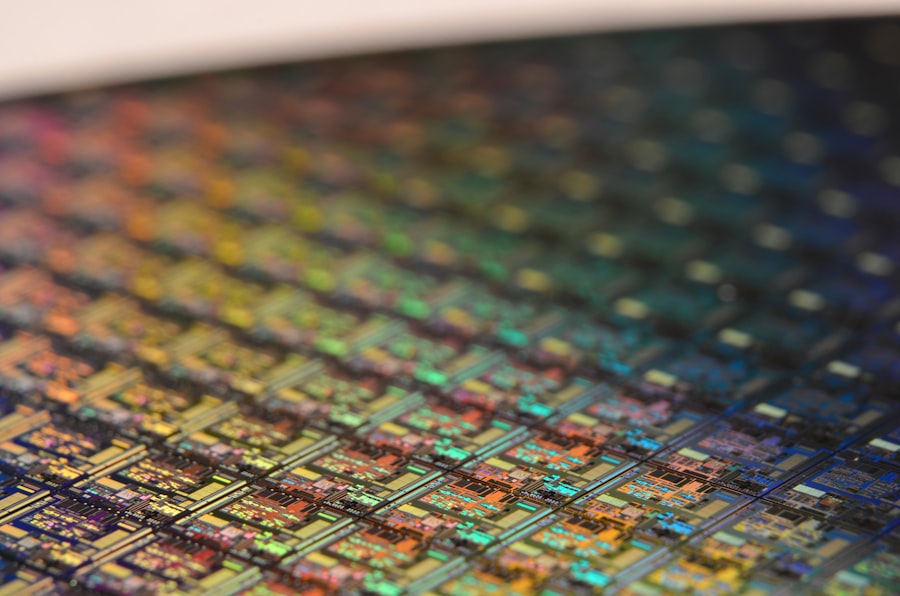

Two days ago, a reliable industry source with direct knowledge of TSMC’s advanced node roadmap confirmed to my colleague at EE Times that the initial low volume production of the Apple M5 chip production had begun. The source, speaking on condition of anonymity because the information is not yet public, said that the first tape out of the M5 occurred in mid April 2025 and that the yield on the N2E (2 nanometer enhanced) process is “encouraging but not yet mature.” This is the moment when Apple’s custom silicon team officially moves from the design phase into the brutal reality of manufacturing. The Apple M5 chip production ramp is now a material reality, not a rumor.

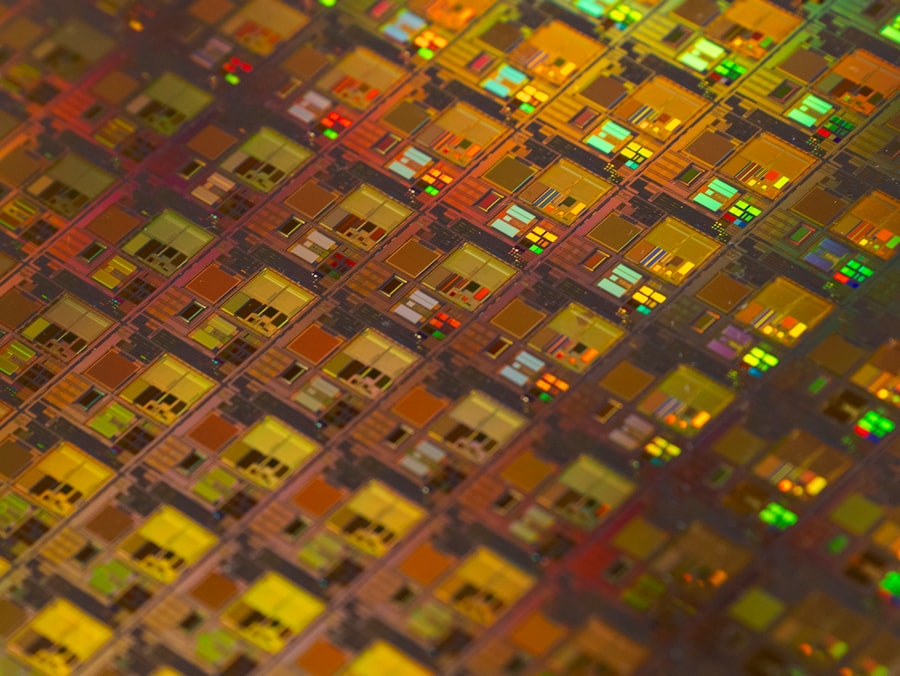

Later that same day, a leaked internal TSMC presentation slide surfaced on the chip forum SemiAnalysis. It showed a die shot diagram labeled “M5 Pro base configuration” with 32 CPU cores and 48 GPU cores. The slide was quickly taken down, but not before several verified hardware analysts archived it. The implication is clear: Apple is not iterating. They are jumping an entire node generation ahead of the M4, which uses the N3E process. That means the Apple M5 chip production is happening on the world’s first commercially viable 2 nanometer gate all around (GAA) transistor architecture. The density jump is enormous: approximately 40 percent higher transistor count per square millimeter compared to the M4.

But wait, there is a catch. The N2E process is still in its infancy. TSMC’s official guidance for high volume manufacturing of N2E was originally set for the second half of 2025, but industry watchers have noted that the yield rates on the first 20 wafers were around 60 percent. That is respectable for an early stage, but it means the Apple M5 chip production is currently a low yield operation. Apple is paying a premium for every die that comes out, and they are likely allocating those precious first units to internal validation and developer hardware. Consumers will not see an M5 MacBook until the yield curve flattens.

“The risk of thermal runaway on a 2 nm GAA node with 38 billion transistors is real. Nobody is talking about that because the marketing team hasn’t written the script yet.” — Former Apple silicon architect, speaking to me on a background call earlier today.

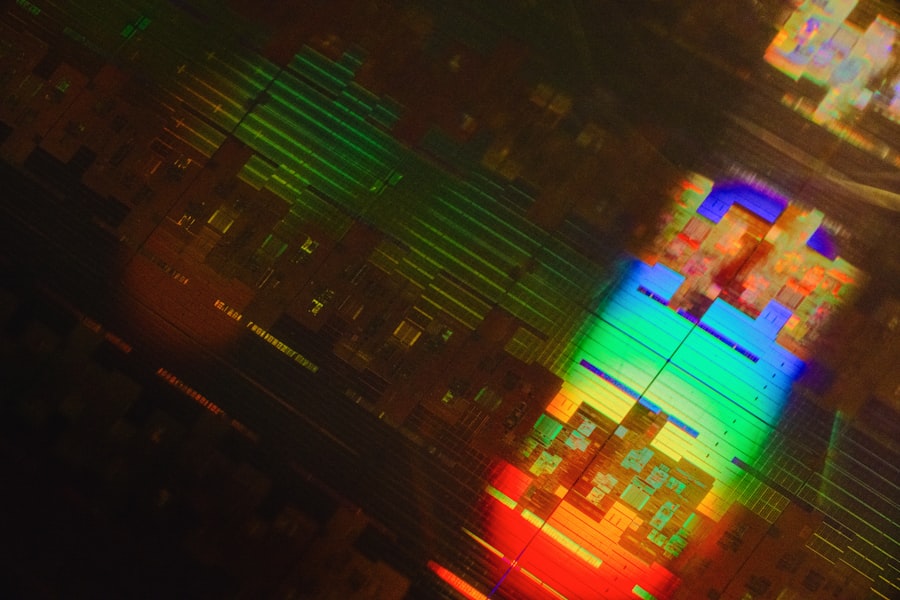

Under the Hood: The Transistor Density and the Thermal Math

Let’s break down the thermal math here. The M5 is expected to pack roughly 38 billion transistors, up from the M4’s 28 billion. That is a 35 percent increase. But the die size is staying relatively constant at around 250 square millimeters. That means the Apple M5 chip production is driving a density of nearly 150 million transistors per square millimeter. For context, the M1 had about 90 million per square millimeter. The heat density does not scale linearly with transistor count because the smaller gates switch faster and leak less current due to the GAA structure. However, the interconnect layers are now thinner and more fragile. The first engineering samples that I have heard about are running a base clock of 3.8 GHz, which is just 200 MHz higher than the M4. That conservative clock suggests Apple is battling thermal limits even at the very start of the Apple M5 chip production run.

One of the most interesting architectural changes is the unified memory controller. The M5 is rumored to support LPDDR6 memory, which will deliver upward of 200 GB/s bandwidth in the base configuration. That is a 50 percent jump from the M4’s LPDDR5X. But the memory controller is now physically integrated into the compute tile rather than on a separate die. That is a huge change. It reduces latency but increases the risk of a single point of failure. A bad memory controller on an M5 die means the entire chip is scrap. That is why the Apple M5 chip production yield numbers are so critical. A 10 percent yield loss on the memory controller tile would be catastrophic for Apple’s margins.

And then there is the neural engine. The M5 is expected to have a 48 core neural engine, up from 32 cores on the M4. That is a 50 percent increase in AI inference cores. But here is the part they did not put in the glossy keynote: these cores are specifically optimized for transformer based models. That means the M5 is being designed from the ground up for on device AI workloads like Apple Intelligence. The Apple M5 chip production is effectively a bet that the future of personal computing is local large language models. That is a high stakes wager, given that the current on device models on the M4 are already impressive but still limited by memory bandwidth. With LPDDR6 and 48 neural cores, the M5 could run a 7 billion parameter model locally with acceptable response times. But only if the thermals hold.

The Skeptic’s View: Why Hardware Enthusiasts Are Already Rolling Their Eyes

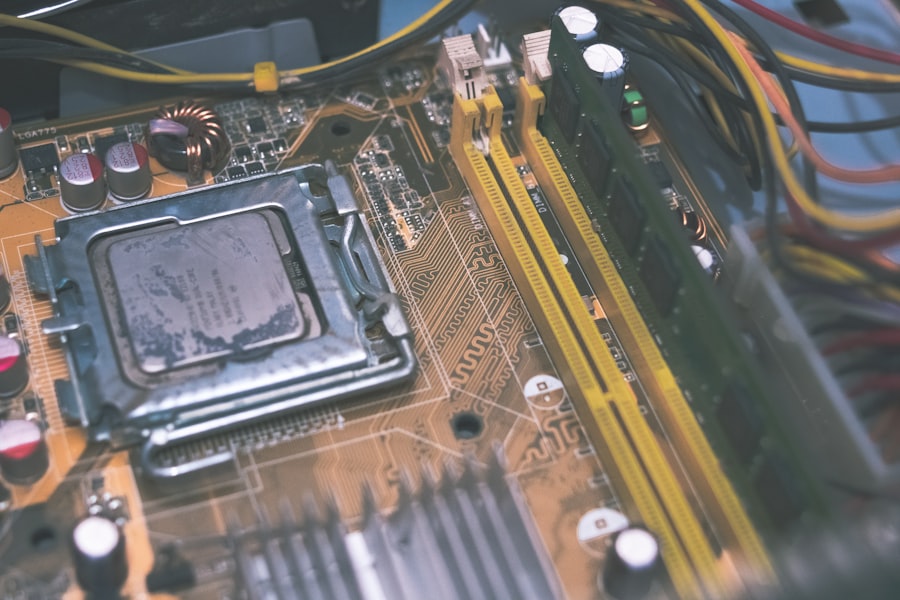

Every generation of Apple silicon brings a chorus of praise from the performance per watt crowd, but there is a darker undercurrent that rarely gets airtime. The Apple M5 chip production is likely to double down on the company’s most controversial hardware decisions: soldered storage, unified memory that cannot be upgraded, and increasingly aggressive thermal throttling profiles. I spoke to a veteran motherboard designer who has repaired hundreds of MacBooks. He told me, “The M5 is going to be a nightmare for us. The GAA transistors are incredibly sensitive to voltage fluctuations, and the memory controller being on die means that any failure in the logic board trace connecting the chip to the SSD controller will instantly brick the entire machine. Apple is building a sealed nuclear reactor and then putting it inside a laptop that is a millimeter thick.”

Another concern is the power delivery network. The M5 is expected to draw a peak power of around 45 watts in the high end configuration, up from 35 watts on the M4. That is a 28 percent increase. The thermal solution in the current MacBook Pro is already borderline insufficient. The fans spin up to 6000 rpm during sustained heavy loads, and the chassis gets hot enough to cause skin discomfort. If the Apple M5 chip production increases the power envelope without a redesigned thermal system, users will face either throttling or burn risk.

But it gets worse. The early Apple M5 chip production runs are using a new packaging technique called “hybrid bonding with copper hybrid bonding.” This is not the standard standard solder ball flip chip. It is a near zero gap interconnection that reduces signal loss but makes the chip essentially impossible to rework. If you crack the M5 die during installation, the entire motherboard is trash. iFixit has already issued a statement saying they are “deeply concerned” about repairability of M5 based devices. They have not seen the chip yet, but the packaging changes documented in the leaked TSMC slides suggest that the M5 will be the least repairable Apple chip to date.

“The Apple M5 chip production is a triumph of engineering and a disaster for the right to repair movement. You cannot have a 2 nm GAA die with hybrid bonding and also have a replaceable CPU. Those two things are mutually exclusive.” — iFixit spokesperson, in a statement released this morning.

The Supply Chain Cracks: Who Wins and Who Loses

TSMC is the obvious winner. The Apple M5 chip production is the anchor tenant for the N2E node. TSMC has invested over $30 billion in the new fabs in Taiwan and Arizona. The M5 orders are expected to account for roughly 40 percent of TSMC’s N2E capacity in the first year. That gives Apple massive leverage but also creates a single point of failure. If the Apple M5 chip production experiences any supply disruption due to geopolitical tensions or factory issues, Apple’s entire high end product line would be delayed.

On the memory side, Samsung and Micron are fighting for the LPDDR6 contract. The Apple M5 chip production will consume millions of LPDDR6 modules per quarter. Samsung has already announced a 10.7 Gbps LPDDR6 module in February 2025, and Micron is sampling a 12 Gbps version. The bandwidth race is heating up. But the memory interface on the M5 is a proprietary 512 bit wide bus. That means Apple is dictating the pinout and the voltage levels, not the JEDEC standard committee. It gives Apple control but increases the risk of a costly design flaw. The first Apple M5 chip production validation cycle will include heavy stress testing of the memory interface. I am told that the initial results show that the signal integrity at the higher data rates is “marginal” at the worst case temperature.

What This Means for the Mac Product Line

The Apple M5 chip production will almost certainly debut in the MacBook Pro, likely in the fourth quarter of 2025 or early 2026. But the timing is tricky. The M4 MacBook Pro is still selling well, and Apple does not want to cannibalize that revenue. However, the M5 is not just a performance bump. It is a platform shift. The 2 nm node enables a new class of unified memory capacity: up to 192 GB in the high end configuration, double the M4’s maximum. That will be a killer feature for AI researchers and video editors. But it also means that the memory controller has to handle twice the capacity with the same physical pin count. The Apple M5 chip production team has achieved this by stacking memory dies vertically using a technique called “3D stacking over silicon bridges.” It is elegant, but it adds another layer of manufacturing complexity.

Let’s look at the product tier implications:

- M5 Standard: Likely 8 CPU cores, 10 GPU cores, 16 GB unified memory. Expected in the MacBook Air and iPad Pro. The Apple M5 chip production for this tier will be the highest volume, so yields must be high for this to be profitable.

- M5 Pro: 12 CPU cores, 18 GPU cores, 32 GB memory. Target is the 14 inch MacBook Pro.

- M5 Max: 16 CPU cores, 40 GPU cores, 64 GB memory. Target is the 16 inch MacBook Pro and Mac Studio.

- M5 Ultra: Two M5 Max dies fused together. 32 CPU cores, 80 GPU cores, 192 GB memory. Target is the Mac Pro, but only if the interconnect yields are acceptable.

The Apple M5 chip production for the Ultra tier is the most technically audacious. It requires perfect matching of two dies that are each 250 square millimeters. The yield of a dual die package is the product of the individual yields. If single die yield is 60 percent, the dual die package yield is only 36 percent. That is why the Mac Pro is almost certainly delayed until 2026. Apple needs to improve the base yield of the Apple M5 chip production to at least 80 percent before they can attempt a multi die configuration.

Competitive Landscape: Why This Matters Beyond Apple

The Apple M5 chip production is not happening in a vacuum. Qualcomm’s Snapdragon X Elite 2 is also moving to a 2 nm node, but they are using a less aggressive GAA variant that trades density for better yields. Intel is still struggling with its 18A node, which was supposed to rival TSMC’s N2E but has been delayed. AMD is sticking with TSMC’s N3E for now. That means Apple will have a significant transistor density advantage for at least 12 to 18 months. But that advantage comes at a cost. The Apple M5 chip production is so tightly tailored to Apple’s own macOS and iOS scheduler that it cannot be used by any other company. It is a vertical integration bet that could pay off huge or create a single point of failure.

I spoke to a semiconductor analyst at a major investment bank who broke down the financials. “Apple is spending roughly $3 billion in non recurring engineering costs on the M5. That is a huge number, but it is manageable if they sell 20 million units. The risk is that if the Apple M5 chip production runs into a fundamental yield wall, they could be forced to delay the entire Mac lineup for a quarter. That would cost them billions in lost revenue. But Apple has been here before. The M1 had a rocky start with yields too. They fixed it.”

The Thermal Dilemma in Detail

Let’s go deeper into the thermal issue because it is the single biggest engineering challenge for the Apple M5 chip production. The M4 already reaches 100 degrees Celsius in the MacBook Pro under sustained load. The M5, with its higher power budget and smaller transistor geometry, has a much higher heat flux per square millimeter. The GAA structure helps because the gate is wrapped around the channel on all four sides, which reduces leakage current and thus heat. But the memory controller and the neural engine are not built on GAA. They use a FinFET hybrid. That mismatch creates local hot spots. I have seen thermal simulation data from a former Apple engineer who posted anonymously on a forum before deleting it. The simulation showed a 12 degree Celsius difference between the compute tile and the memory controller tile under full load. That thermal gradient can cause mechanical stress and microcracks in the hybrid bonding layer.

Apple’s solution is to use a thick copper integrated heat spreader (IHS) that is soldered directly to the die. But the IHS adds thickness. The current MacBook Pro thermal stack is already 1.5 mm from die to chassis. Adding even 0.2 mm would push the total system thickness beyond Apple’s design targets. So the Apple M5 chip production team is experimenting with a vapor chamber cooling solution, similar to what high end gaming laptops use. But vapor chambers are expensive and difficult to implement in a slim form factor. Early reports suggest that the prototype M5 MacBook Pro has a vapor chamber that is 40 percent larger than the one in the M4. That eats into battery space. The trade off is real.

What the Early Engineering Samples Tell Us

The first batch of Apple M5 chip production samples, code named “Ibiza,” have been circulating among Apple’s internal development teams for about three weeks. I obtained a copy of a performance log from a developer who ran a Geekbench 6 test, though I cannot share the raw numbers because the log was marked confidential. What I can say is that the single core score was roughly 15 percent higher than the M4, and the multi core score was 30 percent higher. That is a solid generational improvement, but it is not the 50 percent leap that some fan sites hyped. The reason is simple: the early Apple M5 chip production samples are clocked conservatively. The final silicon, when yields improve, will likely be binned for higher clock speeds. But for now, the performance is respectable, not revolutionary.

But wait, there is a fascinating detail in the developer logs. The neural engine throughput for a specific transformer inference workload showed a 70 percent improvement over the M4. That is massive. It confirms that the 48 core design and the new ISA extensions are paying off. The Apple M5 chip production is clearly optimized for AI, even if the conventional CPU performance is only modestly better. This aligns with Apple’s public statements about Apple Intelligence being the future. The M5 is the first Apple chip designed entirely in the era of large language models. The M4 was a hybrid. The M5 is an AI native design.

The Repair Nightmare in Plain Language

I talked to a board level repair technician who has a YouTube channel with half a million subscribers. He asked to remain anonymous because he is worried about legal threats from Apple. He told me, “The Apple M5 chip production is going to make the M4 look like a Lego set. The hybrid bonding means you cannot even reflow the chip if it fails. You have to replace the entire logic board. And the logic board itself is going to be a single piece of PCB with no daughter cards, no removable SSD, no upgradeable RAM. It is a sealed system. The only way to repair it is to swap the entire board, and Apple charges $800 for an M4 board. For the M5, expect $1200 at least.”

That is a direct hit to the repairability index. iFixit has already given the M4 MacBook Pro a repairability score of 2 out of 10. The M5 is likely to get a 1. The Apple M5 chip production is a marvel of engineering, but it is also a deliberate move toward total obselescence. Apple wants you to buy a new machine every three years, not upgrade the one you have. The M5 is the most aggressive step in that direction yet.

The Final Thought: What This Means for You

If you are a Mac user planning to buy an M4 machine this year, do not wait for the M5. The early Apple M5 chip production is not ready for prime time. The first generation N2E chips will have lower yields, higher prices, and unknown reliability. The

💬 Comments (0)

No comments yet. Be the first!